Le besoin est d'avoir un signal d'horloge propre mais à fréquence variable, avec un ratio de 50%. Il doit également pouvoir être débrayable pour passer en mode pas-à-pas sans rebond bien sûr, que ce soit à chaque pas ou lors du changement de mode.

En bonus, il serait intéressant de fournir un signal RESET propre qui est activé à la mise sous tension et à chaque fois qu'on appuie sur le bouton RESET.

Notes :

- Chaque signal est fourni en logique positive (actif à l'état haut) et négative (actif à l'état bas)

- Le RESET et le signal d'horloge sont indépendants ce qui signifie que le RESET n'interrompt pas l'horloge.

Ce montage doit rester simple à réaliser (pas de micro-contrôleur par exemple) et fournir une fréquence d'horloge assez lente, disons entre 1 et 100Hz environ, afin de pouvoir montrer le fonctionnement de composants utilisant de la logique séquentielle. Mais regardons comment j'ai fait.

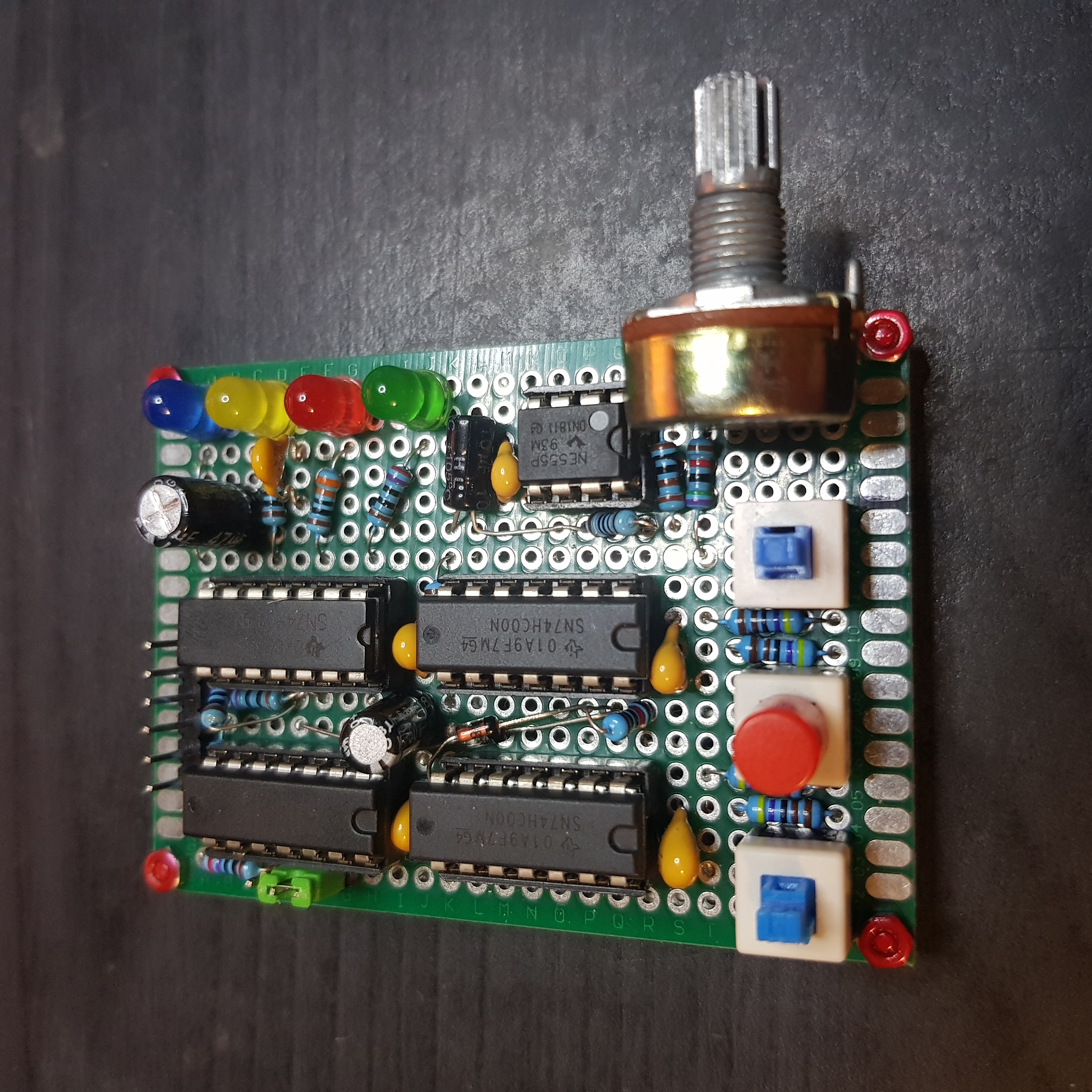

Réalisation

Le schéma général est disponible ci-dessous :

L'oscillateur pour générer la fréquence de l'horloge

La génération du signal d'horloge primaire

Pour générer le signal d'horloge, j'ai utilisé le fameux NE555 en mode astable. On trouve très facilement des montages ou des tutos sur le sujet. Je vous propose notamment de regarder ces 2 vidéos de Thonain sur la Tronik Aventur:

- Tronik Aventur n°66 - NE555 Partie 1 - Électronique débutants Oscillateur

- Tronik Aventur n°67 - NE555 Partie 2 - Pour débutant - Comment ça marche

Rien d'innovant dans le montage utilisé pour ça :

Oubliez le connecteur J1, il permet de pouvoir mettre le potentiomètre en façade facilement si nécessaire (dans ce cas, il remplace RV1). Les broches 2 et 6 sont reliées entre-elles.

Le principe est simple :

- Le condensateur C2 se charge via les résistances R5 et R6 et le potentiomètre RV1 monté en résistance variable. RV1 permet d'ajuster le temps nécessaire pour que C2 se charge

- Lorsque la tension aux bornes du condensateur C2, donc celle entre les bornes 2 et 6 du NE555 par rapport à la masse (GND) atteint ⅔ de VCC, le NE555 bascule

- La sortie CP (broche 3) s'inverse et le NE555 lance la décharge du condensateur via DIS (broche 7) et R6.

- Lorsque la tension aux bornes du condensateur C2 atteint ⅓ de VCC, le NE555 bascule à nouveau et on repart à l'étape 1

Ce montage modifie le temps de charge du condensateur, mais pas le temps de décharge, cela va donc faire varier le ratio.

Le ratio (aussi appelé duty cycle en anglais) est le rapport entre la durée à l'état haut et la période totale. Un ratio à 100% correspond à un signal toujours à l'état haut. Un ratio à 0% correspond à un signal toujours à l'état bas. On cherche un ratio à 50%, c'est à dire que le signal reste la moitié du temps à l'état haut, l'autre moitié du temps à l'état bas. Mais on va voir après comment garantir un ratio de 50% facilement.

Pour les matheux, on peut calculer la fréquence du NE555 avec la formule suivante :

Ici, RV1 varie entre 0 et 50 kΩ, donc la fréquence varie entre 48 Hz et 2,7 Hz respectivement. Il est possible d'étendre la plage de fréquence en utilisant un potentiomètre de 100 kΩ par exemple, voir plus.

Génération d'un signal carré avec un ratio de 50%

Pour cela, encore une fois, j'ai utilisé une méthode très simple qui consiste à injecter le signal généré par le NE555 à l'entrée d'une bascule D.

Si on relie la sortie inversée (souvent notée Q) à l'entrée de la bascule D (souvent notée D), la sortie normale (souvent notée Q) va alterner à chaque top d'horloge. Donc seule la fréquence des tops d'horloge en entrée compte, la sortie de la bascule ne dépend pas du tout du ratio du signal en entrée. Cela permet de garantir un ratio à 50% mais cela divise la fréquence par 2.

J'ai utilisé le circuit intégré 74HC74 qui contient 2 bascules D avec SET et RESET qui bascule lors du front montant des tops d'horloge.

Philippe Demerliac a fait une très bonne vidéo sur les bascules sur sa chaîne Cyrob : Cyrob : Logique 4 les bascules RS, D, JK et compagnie..

On va voir plus loin comment j'utilise R (RESET actif bas) et S (SET actif bas) pour le mode pas-à-pas, mais on va considérer ici qu'ils sont tous les deux à l'état haut, donc inactif. Dans le datasheet de Texas Instruments, on peut voir la table de vérité suivante :

On remarque que chez Texas Instruments l'entrée RESET s'appelle CLR (et R sur mon schéma), l'entrée SET est notée PRE (et S sur mon schéma). Pour l'instant seules les 3 dernières lignes nous intéressent. On voit que si D est connecté à Q, la sortie D va osciller entre H (haut) et L (bas) à chaque fois qu'un front montant (↑) se présente sur l'entrée d'horloge (notée CLK chez Texas Instruments et C dans mon schéma).

On note aussi que Q et Q sont opposés : lorsqu'un est à l'état haut (H), l'autre est à l'état bas (L) et réciproquement.

L'avantage ici est que les sorties Q et Q sont en phase, il n'y a pas de décalage entre ces deux sorties.

Le mode pas-à-pas

Pour ce mode, on va utiliser les entrées CLR et PRE de la bascule D car on voit qu'ils permettent de forcer la sortie de la bascule soit à l'état bas, soit à l'état haut.

Le problème qui se présente ici c'est de supprimer les rebonds du bouton poussoir.

Pour ça j'ai utilisé une bascule RS constituée de deux portes NAND comme on peut le voir ci-dessous :

Les sorties STEP et STEP sont inversées et correspondent à la position du bouton poussoir inverseur (SW2), les rebonds en moins.

Philippe Demerliac explique bien sur sa chaîne Cyrob ce que sont les rebonds et comment y remédier dans la vidéo Cyrob : Rebond des contacts, cause et remèdes.

Il faut maintenant pouvoir passer du mode pas-à-pas au mode horloge à fréquence variable. On a vu qu'en mode pas à pas, on met une seule des entrées CLR et PRE de la bascule D à l'état bas, alors qu'en mode "normal" ces deux entrées sont à l'état haut.

Pour ça nous allons utiliser les deux autre portes NAND qui sont dans le 74HC00 :

Cela donne la table de vérité suivante :

| SW2 | HOLD | STEP | STEP | R | S | Note |

| relâché | H | L | H | H | L | Mode pas-à-pas, horloge à l'état haut |

| enfoncé | H | H | L | L | H | Mode pas-à-pas, horloge à l'état bas |

| relâché | L | L | H | H | H | Mode normal, la position de SW2 est ignorée |

| enfoncé | L | H | L | H | H |

Changer proprement entre le mode pas-à-pas et normal

Pour ça il suffit d'utiliser un interrupteur RT (repos/travail), aussi appelé SPDT en anglais (pour Simple Pole, Double Throw) suivi d'une bascule RS pour se protéger des rebonds, exactement comme on vient de voir.

Le mode RUN est le mode normal : l'horloge à fréquence variable est fourni en sortie. Le mode HOLD est le mode pas-à-pas. Notez qu'il s'appelle comme ça car il permet aussi de mettre simplement en pause le signal d'horloge en sortie si on n'appuie pas sur le bouton SW2.

Maintenant, il nous reste une bascule D de disponible dans le boîtier U5. On peut l'utiliser pour ne changer de mode qu'entre 2 tops d'horloges pour conserver un signal stable sur l'autre bascule D lors des fronts montant de l'horloge.

Pour ça nous allons utiliser le signal d'horloge généré par le NE555 mais le mode ne doit changer que lorsque l'horloge est à un état stable en sortie (disons l'état bas, de façon totalement arbitraire).

Si les deux bascules D basculent en même temps on peut avoir des artéfacts en sortie. Supposons par exemple que la première bascule D fait passer le signal d'horloge en sortie à l'état haut et qu'au même moment l'autre bascule D prend en compte le passage en mode pas-à-pas avec une horloge en sortie à l'état bas. Avec les temps de propagation, on peut se retrouver avec un signal de sortie contenant un pas parasite très bref.

Pour éviter cela, il suffit de changer les 2 bascules l'une après l'autre et non en même temps. Mais nous avons qu'une seule horloge en entrée (la sortie du NE555). Il faudrait par exemple qu'une des bascule D change lors du front montant de l'horloge et l'autre lors du front descendant. Mais c'est dommage d'utiliser un deuxième circuit intégré et de ne pas utiliser la bascule D inutilisée du premier.

Il existe une solution très simple pour changer le front d'entrée, il suffit d'utiliser un inverseur :

Ici nous ne forçons pas les entrées SET et RESET mais on inverse le signal d'horloge venant du NE555. Il reste un dernier point : il ne faut passer au mode pas-à-pas que lorsque l'horloge est à l'état bas et rester dans ce mode tant que l'interrupteur est dans la position pas-à-pas (HOLD).

HOLD_RDY détermine le mode qu'il va y avoir au prochain cycle d'horloge, il doit être égal à (HOLD_REQ ET (CLK OU HOLD)).

Il est très facile de faire une porte OU avec 2 diodes et une résistance de pull-down. Si une des entrées au moins est à l'état haut, la ou les diodes correspondantes deviennent passant et on a un état haut ; sinon aucune des diodes n'est passante et on est à l'état pas. Cela permet de faire le OU entre CLK et HOLD. Reste le ET logique. Pour ça, il nous reste deux portes NAND inutilisées. Si on relie les entrées d'une porte NAND, on obtient une porte inverseuse (ou porte NON ou NOT). Or une NAND suivie d'une NOT fait une porte AND (ET). Cela nous donne ce schéma :

L'entrée HOLD_REQ est à l'état haut lorsque l'interrupteur SW1 est en position pas-à-pas. CLK est à l'état haut lorsque CLK est à l'état bas. HOLD est à l'état haut lorsqu'on est déjà en mode pas-à-pas.

Et voilà, nous avons toutes les briques du puzzle.

Mesures à l'analyseur logique

On voit que :

- On a un signal d'horloge primaire (la sortie du NE555, 2CLK sur le graphe) qui a un ratio proche de 100% et donc loin des 50% mais cela ne pose pas de souci car après le passage par la bascule D, la sortie CLK a bien un ratio de 50% avec la moitié de la fréquence primaire.

- Le passage en mode pas-à-pas (passage de RUN de l'état haut à l'état bas) ne se fait qu'au prochain top d'horloge après avoir enfoncé l'interrupteur SW1 (RUN_REQ sur le graphe)

- Les appuis sur le bouton poussoir SW2 sont biens sans rebonds mais ils ne sont pris en compte que lorsqu'on est en mode pas-à-pas et sont alors directement reportés sur la sortie CLK. Par contre, en mode RUN (mode normal), ils sont ignorés.

La gestion du RESET

On veut un signal RESET à la mise sous tension ainsi qu'à chaque appui sur un bouton poussoir. Ce signal doit être actif pendant un minimum de temps garanti et resté actif dans que le bouton est enfoncé.

Rappel : ce circuit n'a aucune interaction avec l'horloge créée juste au dessus.

Il aurait été possible d'utiliser un autre NE555 ou encore des circuits spécialisés.

Ici j'ai choisi la simplicité en profitant d'un des défaut d'un montage anti-rebond à base d'un inverseur à hystérésis et du chargement d'un condensateur :

L'avantage de ce circuit, il est simple et correspond à tous les critères du cahier des charges :

- À la mise sous tension, le condensateur C4 est déchargé. Il se charge via R8 et R9. Tant que la tension aux bornes du condensateur C4 est inférieure au seuil de basculement de la porte inverseuse à trigger de Schmitt, celle-ci reste à l'état haut. Elle passe à l'état bas dès que la tension est suffisante. Le fait d'utiliser un trigger de Schmitt garanti un passage franc d'un état à l'autre. Donc le RESET est bien actif à la mise sous tension.

- Lorsqu'on appuie sur le bouton RESET, cela décharge le condensateur via R9. La résistance R9 permet de limiter le courant de décharge pour éviter les arcs au niveau du bouton poussoir et ainsi de l'endommager mais également d'éviter des courants de décharge trop important au niveau du condensateur. Avec une résistance de 10 Ω, on s'assure que le courant ne dépassera pas 500 mA tout en garantissant une décharge rapide du condensateur (τ=RC=10×6,8×10-6=68 µs). Tant que le bouton reste enfoncé, le signal RESET reste actif.

- Dès qu'on relâche le bouton, le condensateur se recharge comme lors de la mise sous tension et garanti le même délai minimum.

OK, mais à quoi sert D2 ? Ce montage est fait pour fonctionner avec différentes technologies, que ce soit du CMOS ou du TTL par exemple. Si la porte logique dispose d'une entrée haute impédance, lorsque le courant est coupé, C4 reste chargé (car aucun courant ne circulera en entrée de la porte logique). De plus, certains circuits intégrés n'aiment pas avoir une tension sur leurs entrées (tensions de C4) qui soit supérieure à la tension d'alimentation (ici 0V). La diode D2 permet alors de décharger le condensateur lorsque l'alimentation est coupée.

Note : il y a généralement des diodes de protection sur les entrées CMOS, dans ce cas la diode interne peut jouer ce rôle. Mais en cas de court-circuit franc de l'alimentation, le courant de pic sur ces diodes internes peut être excessif c'est pourquoi je conseille de garder cette diode externe.

Ensuite, on voulait aussi avoir une sortie RESET active à l'état bas. Pour ça il suffit d'ajouter une autre porte NON. Cela va introduire un retard (< 25 ns) entre les deux signaux RESET, mais je l'ai considéré comme acceptable pour ce genre de signal.

Les fichiers de ce projet sont accessibles uniquement aux personnes connectées.

N'hésitez pas à commenter !